TSMC to start eMRAM production in 2018

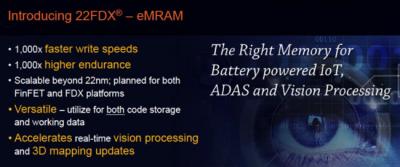

According to reports, Taiwan Semiconductor Manufacturing Company (TSMC) is aiming to start producing embedded MRAM chips in 2018 using a 22 nm process. This will be initial "risk production" to gauge market reception.

TSMC also aims to start embedded RRAM chip production in 2019.