CEA-Leti and NY CREATES to co-develop STT-MRAM and SOT-MRAM devices on 300 mm wafers

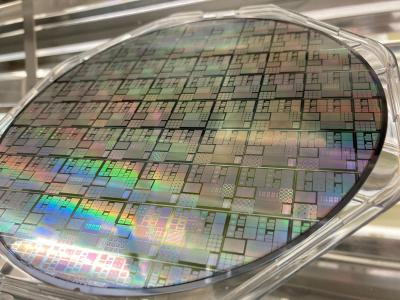

The New York Center for Research, Economic Advancement, Technology, Engineering, and Science (NY CREATES) and CEA-Leti announced a two-year strategic R&D partnership, that will initially focus on the research and co-development of MRAM devices.

NY CREATES and CEA-Leti will develop and produce both STT-MRAM and SOT-MRAM devices on 300 mm substrates. CEA-Leti will contribute its expertise in magnetics, spintronics, and the testing of related devices, and NY CREATES will provide the facilities, process integration expertise, and materials process development to run the 300mm silicon hardware.

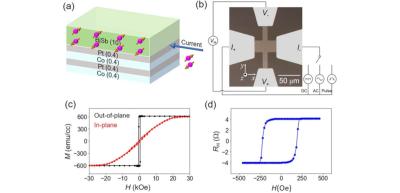

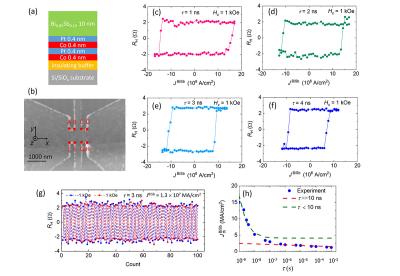

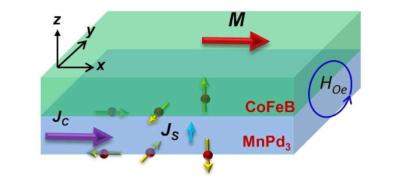

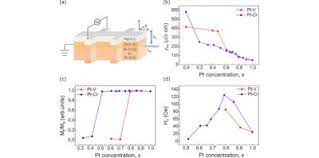

The new device is based on 3d light transition metals (such as V and Cr) that are incorporated into the classical spin Hall metal Pt. The Pt-Cr alloy enhances the charge-to-spin conversion efficiency which can realize high spin-orbital Hall conductivity, beyond the conventional spin Hall limit.

The new device is based on 3d light transition metals (such as V and Cr) that are incorporated into the classical spin Hall metal Pt. The Pt-Cr alloy enhances the charge-to-spin conversion efficiency which can realize high spin-orbital Hall conductivity, beyond the conventional spin Hall limit.