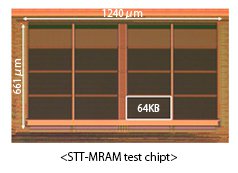

Spin Transfer Technologies produced working 60-nm STT-MRAM prototypes

Spin Transfer Technologies (STT) has successfully produced a working prototype STT-MRAM device. The company's advanced prototyping magnetics processing line at its facility in Fremont, California, is now fully operational.

Spin Transfer Technologies (STT) has successfully produced a working prototype STT-MRAM device. The company's advanced prototyping magnetics processing line at its facility in Fremont, California, is now fully operational.

STT's prototypes incorporate proprietary, performance-enhancing âspin-filteringâ technology, and were fabricated on industry standard CMOS wafers sourced from a high volume Asian foundry supplier. The prototypes are based on 60-nm perpendicular magnetic tunnel junction devices