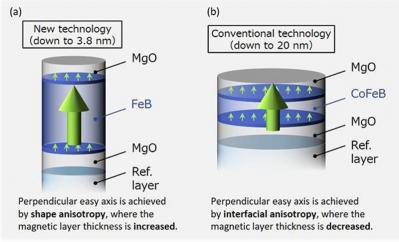

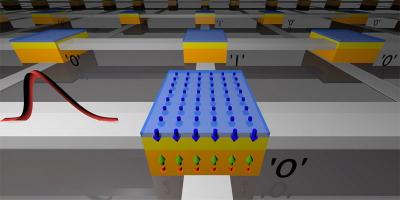

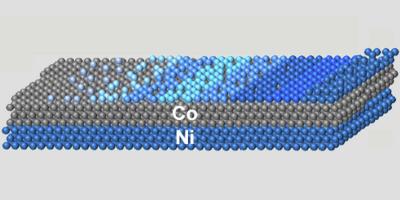

Multi-layered Co/Ni films are highly desirable materials for effective spin transfer torque

Researchers from the University of Lorraine in France have discovered that multilayers films made of cobalt (Co) and nickel (Ni) hold great promise for STT-MRAM applications.

It was already shown before that Co/Ni multilayers have very good properties for spintronics applications, but up until now it wasn't clear if the films have a sufficiently large intrinsic spin polarization, which is necessary to create and maintain spin-polarized currents in spintronic devices. It was now shown that the films have a spin polarization of about 90% - which is similar to the best spintronic materials.