In 2015, the EU launched the GREAT project, with an aim to co-integrate multiple functions like sensors, RF receivers and logic/memory together within CMOS by adapting STT-MTJs to a single baseline technology in the same system on chip. GREAT stands for heteroGeneous integRated magnetic tEchnology using multifonctionnal stAndardized sTack.

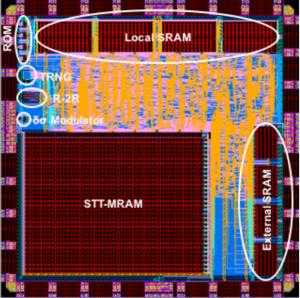

After the delivery of a first demonstrator in 2017, the project partners now announced the second hybrid CMOS/MSS-MRAM 180nm Tape Out at Israel-based Tower Jazz. The project partners designed four ICs to validate Analog IP blocks and an ultra-low power MCU comprising a hardware security block.

The GREAT project developed an ultra-low power normally-off MCU based on 32-bit non-volatile processor core. The processor core features:

- A non-Volatile flip flop

- A Non-volatile controller with wake-up and backup recovery and Instant on-off capabilities

- SRAM and STT-MRAM memories

- Secure block based on the MSS stack (cryptographic keys generation)

- A set of Analog IP blocks

The next phase of the project is test all the IC and characterize the hybrid CMOS/MRAM process. Results are expected by the second quarter of 2019.

The GREAT project partners inclues CEA Spintec, Karlsruhe Institute of Technology (KIT), Laboratoire d'Informatique, de Robotique et de Microélectronique de Montpellier (LIRMM), Universitatea Transilvania din Brasov (UTBV), Technische Universität Dresde (TUD), Singulus Technologies AG, Tower Jazz, eVaderis and Toplink Innovation.