Toshiba has developed a prototype memory element for STT-MRAM that (according to Toshiba) achieves the world's lowest power consumption yet reported. STT-MRAM based on this element has the potential to surpass the power consumption efficiency of SRAM as cache memory.

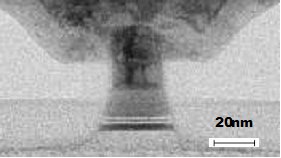

Toshiba's improved structure is based on perpendicular magnetization and takes element miniaturization to below 30nm. Introduction of this newly designed "normally-off" memory circuit with no passes for current to leak into cuts leak current to zero in both operation and standby without any specific power supply management. The company says it improved the speed of their previous design - while reducing the power consumption by 90%.

Toshiba expects their STT-MRAM to be used as cache memory for movile processors, and intends to accelerate R&D towards that goal. Back in November 2011 Toshiba unveiled a hybrid cache design that uses STT-MRAM and SRAM combination, aimed towards next-generation low-power computer processors. The company also discussed using STT-MRAM as cache for HDD and NAND.

The new design was developed as part of the "Normally-off Computing" project funded by Japan's NEDO (New Energy and Industrial Technology Development Organization).