Tohoku University researchers develop the world's fastest STT-MRAM

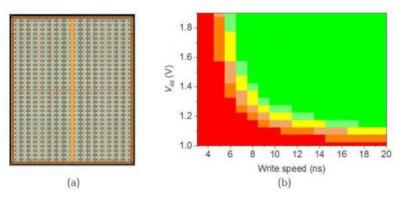

Researchers from Japan's Tohoku University developed a 128 Mb STT-MRAM device that features a write speed of 14 nm, the world's fastest STT-MRAM chip at a density over 100 Mb.

To achieve this high speed, the researchers developed MTJs that are integrated with CMOS, which also significantly reduces the power-consumption of the memory device.