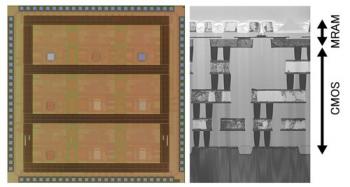

NEC announced the

successful operational demonstration of a 32Mb MRAM that can be embedded in SoCs. NEC has reduced the area of control circuits in the 32Mb MRAM

design in order to achieve superior cell efficiency that enables

73% of a memory macro's area to be allocated to memory cells. This was achieved by developing write circuits, which enables greater memory capacity. The high-speed cycle time of 9ns was achieved by adopting new decoder circuits that minimize delay.

Furthermore,

compatibility with an asynchronous SRAM was achieved by inserting

protocol transform circuits between the MRAM macro and I/O buffer

circuits.

In

November 2007 NEC developed a

high speed 250MHz, 1Mb MRAM macro suitable for embedding in system

LSIs. However, since the memory cell of the high speed 1Mb MRAM macro

consists of two transistors and one MTJ, enlarging its memory capacity

is more challenging than increasing the memory of MRAM macro equipped

with just one transistor and one MTJ cell.

The latest

demonstrations adapted MRAM macro cell arrays with NEC's newly

developed write circuits to achieve macro cell efficiency of 73%. This

both reduced MRAM macro size and enlarged memory capacity.

The

macro's word line decoder circuit was equipped with a word boost

circuit in order to shrink memory cell area. However, word boost

circuits are prone to delay and tend to extend the cycle time of

macros. To solve this problem, a word boost circuit featuring optimized

conversion levels was developed. Accordingly, the high speed operation

cycle time of 9ns was achieved despite being a large capacity 32Mb

macro.

Looking forward, NEC is aiming to demonstrate an SoC integrated

with large capacity, high speed MRAM macros.