Avalanche Technology adds new 2Gb and 8Gb densities of its 3rd-Gen space-grade STT-MRAM

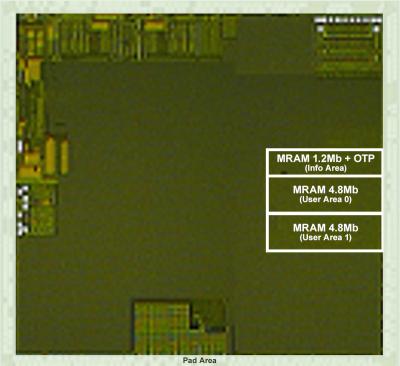

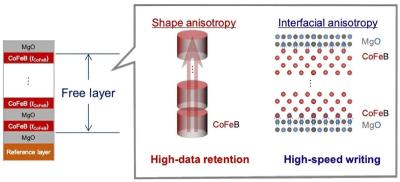

pMTJ STT-MRAM developer Avalanche Technology launched two new densities of its 3rd generation space-grade parallel asynchronous x32-interface high-reliability P-SRAM (Persistent SRAM) memory devices, based on its latest STT-MRAM tech, in 2Gb and 8Gb.

In June 2023 Avalanche announced that it is providing its products for satellite power applications developed by Advanced Space Power Equipment. Earlier that year Avalanche announced that its Gen-3 Space Grade Dual QSPI solution is now available in pre-production.