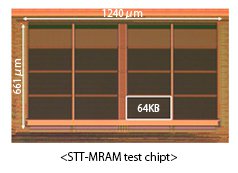

Toshiba presented a new STT-MRAM 1-Mb test chip that provides speed performance capable of 3.3-ns access to in-cache memory. The newly developed circuit consumes about 80% less power compared to a conventional SRAM as embedded memory - and Toshiba says that this makes it the best power-performing embedded memory.

To make this chip, Toshiba developed a new class of magnetic materials, that enabled them to build this low-power, high-efficiency, high-speed performance in energy-efficient magnetic tunnel junction (MTJ) memory.

The circuit was designed for sub-100-ns high-speed power shutoff and restoration and Toshiba confirmed its operation when building the test chip. To reduce the time for power restoration after shutoff, Toshiba divided power shutoff into seven regions, provided power switches for each region, and then allowed power shutoff for regions other than those involved in memory operations. In measured values for the main operational mode, the best time for power restoration was confirmed as 22 ns following power shutoff, which is shorter than the approximately 30 ns average wait time for cache memory access.

Toshiba developed this chip with aid from the Japanese New Energy and Industrial Technology Development Organization. They are now aiming to continue and improve the technology, with an aim to lower the power consumption even further. By the end of Fiscal 2015 (which means March 2016 in Japan), Toshiba hopes to reduce overall processor power consumption to less than one-tenth that of conventional circuits.

In December 2013, Toshiba announced a new computing architecture that uses only STT-MRAM to perform both operations and storage. The idea support computing capability, register file, primary cache and secondary cache all on the same perpendicular STT-MRAM, and Toshiba says it could lead to CPUs that are drastically faster and more efficient. Later in June 2014 Toshiba unveiled new STT-MRAM technology that can be used to enable MRAM based cache memory for microprocessors - and this new achievement seems to be the continuation of this research program.