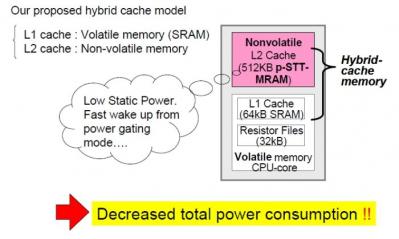

Toshiba has a new hybrid cache design that uses STT-MRAM and SRAM combination. This is aimed towards next-generation low-power computer processors. These new computers will usually be off, and the time and power it takes to "wake up" is considerable. The new design can reduce the energy consumption by around half - and does not effect processing capacity.

Toshiba's design uses a 512Kb STT-MRAM cache combined with a 32Kb register file and a 64Kb SRAM primary cache. Using the non-volatile MRAM, the power gating can be conducted more frequently. In current designs, it takes around 20 micro seconds to recover from power gating and about 150 micro seconds from deep-sleep mode. In the new design, it takes only 1 micro second to recover from power gating.

The STT-MRAM runs at a lower frequency compared to the SRAM, which is why they are proposing a hybrid design and not just MRAM. This isn't the first time Toshiba is discussing the possibility of using MRAM as cache.