Researchers add YSZ layers to MRAM devices to increase efficiency and speed

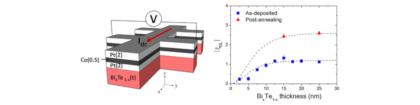

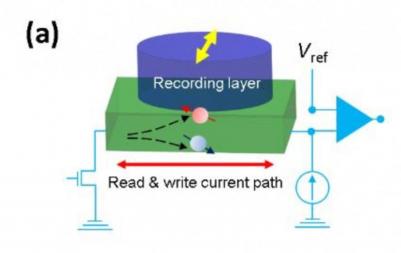

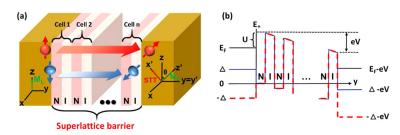

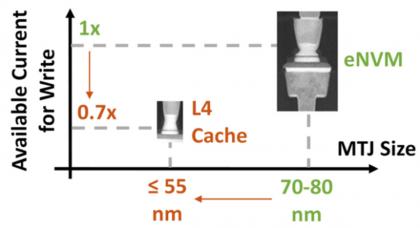

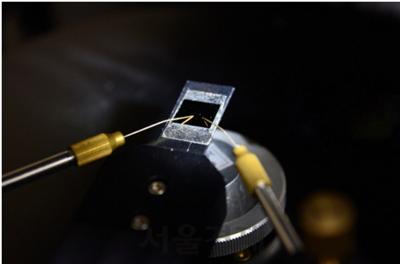

Researchers from the Korea Institute of Science and Technology (KIST) have managed to drastically incraese the speed of MRAM devices while reducing the power consumption by adding a layer of yttria-stabilized zirconia (YSZ) to MRAM devices.

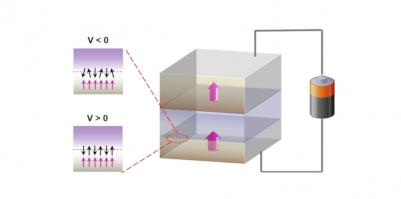

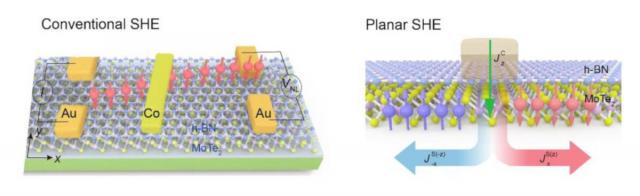

The YSZ layer, which has high ion conductivity helps inject hydrogen ions into the MRAM cell. This resulted in an increase in the speed of the spin alignment direction changes 100-fold.