New USMR MRAM structure promises extremly simple design

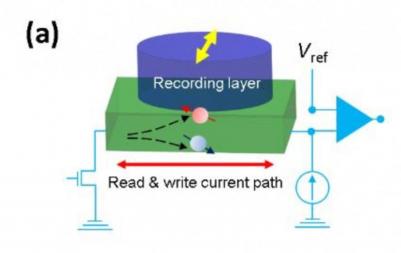

Researchers from Tokyo's Institute of Technology (Tokyo Tech) developed a new MRAM cell structure (called USMR MRAM) that features a very simple structure with only two layers - which could hopefully enable lower-cost MRAM devices.

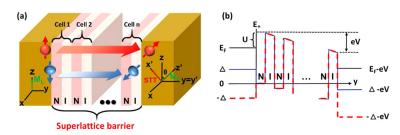

The new design uses a combination of a topological insulator with a ferromagnetic semiconductor which enables a giant unidirectional spin Hall magnetoresistance (USMR).