Everspin Technologies reported its financial results for Q2 2023

Everspin Technologies its financial results for Q2 2023 - with revenues of $15.7 (up 7% compared to 2022), a net income of $3.9 million, and positive cash flow of $3.9 million (which includes a tax credit refund of $2 million). At the end of the quarter, cash and cash equivalents were $30.8 million

The company says that its product backlog into 2024 continues to be high, but the company is experiencing some headwinds from the semiconductor downturn.

A recent breakthrough in spintronics research could lead to faster and more efficient optically-controlled MRAM devices

Researchers from the Hebrew University of Jerusalem in Israel have made a recent discovery that could change the face of spintronics research - the most important equation used to describe magnetization dynamics, namely the Landau-Lifshitz-Gilbert (LLG) equation, also applies to the optical domain.

A spintronics device developed by Professor Capua's lab

The new discovery has relevant applications in optical magnetic recording, namely in optically-controlled MRAM technology. Manipulation of the magnetization order parameter on optical timescales is key for ultrafast spintronics, which allows for faster, energy-efficient optically-controlled MRAM technology.

Avalanche to supply its Gen-2 space-grade MRAM to ASP's satellite power applications

pMTJ STT-MRAM developer Avalanche Technology announced that it is providing its disruptive Space Grade Persistent SRAM (P-SRAM) products for satellite power applications developed by Advanced Space Power Equipment GmbH (ASP).

ASP has designed in a 16Mb device from Avalanche’s Gen 2 Space Grade P-SRAM family into its next-generation Power Conditioning & Distribution Unit (PCDU) within its satellite platform product line.

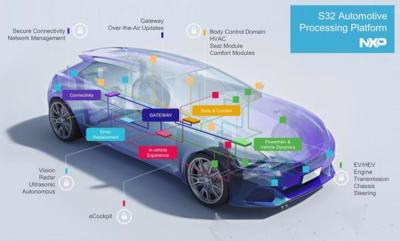

NXP and TSMC to offer 16 nm FinFET automotive embedded MRAM

NXP Semiconductors announced a collaboration with TSMC to offer automotive embedded MRAM, in TSMC's 16 nm FinFET technology. NXP says that as automakers transition to software-defined vehicles, they need to support multiple generations of software upgrades on a single hardware platform. Bringing together NXP’s high-performance S32 automotive processors with fast and highly reliable next-generation MRAM in 16 nm FinFET technology provides the ideal hardware platform for this transition.

The new MRAM memory will be able to udpate 20MB of code in ~3 seconds compared to flash memories that take about 1 minute, which will minimize the downtime associated with software updates. MRAM also provides a highly reliable technology for automotive mission profiles by offering up to one million update cycles, a level of endurance 10x greater than flash and other emerging memory technologies.

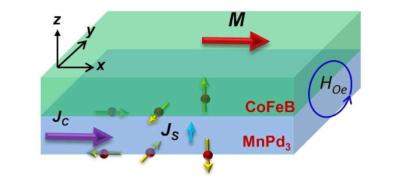

Researchers say MnPd3 will enable a breakthrough in SOT-MRAM memory devices

Researchers from the School of Engineering at Stanford University discovered that a metallic compound called manganese palladium three MnPd3 is a promising material to build SOT-MRAM memory devices.

The researchers say that the new material enables a breakthrough in SOT-MRAM device performance, as it is the first material that generates spin in the z-direction, rather than the y-direction as in most materials, which is a property needed in high-performance SOT-MRAM. In fact MnPd3 is able to generate spins in any orientation because its internal structure lacks the kind of crystal symmetry that would force all of the electrons into a particular orientation.

Everspin reports its financial results for Q1 2023, with continued profit and growth

Everspin Technologies reported its financial results for Q1 2023, with revenues of 14.8 million, at the high end of its guidance and an increase of 3% from 2022. The company's earnings remain positive (now for two years in an row), and cash flow during the quarter was $1.2 million.

The company says that its product backlog for the rest of 2023 and 2024 remains high, and the company is optimistic regarding its sales in the near future.

The company says that its product backlog for the rest of 2023 and 2024 remains high, and the company is optimistic regarding its sales in the near future.

Recent MRAM Industry News, April 2023

Here are some recent and popular news that you may find of interest:

- Everspin launches a new family of SPI interface MRAM products

- Researchers develop sub-volt nanoscale perpendicular VC-MRAM devices

- Everspin to build a new MRAM production line in Indiana

- Renesas develops 22-nm circuit technologies for embedded STT-MRAM

- Samsung first to demonstrate MRAM-based in-memory computing

- Everspin reports excellent financial results in Q4 2022

- IBM to reveal the world's first 14nm STT-MRAM node

- ITRI and UCLA to co-develop VC-MRAM technologies

- Avalanche starts production of its 3rd-Gen 22nm MRAM devices

- Samsung improves its MRAM performance, to expand target applications

- TSMC shows its eMRAM technology roadmap

- Researchers developed the world's smallest STT-MRAM MTJ

- Samsung is progressing towards 14 nm eMRAM

Everspin reports excellent results in Q4 2022, above its high end of guidance

Everspin Technologies announced its financial results for Q4 2022, with revenues of $15.7 million (above the high end of guidance, and up 3% from Q1 2022). The company reported net income of $0.6 million, this is the 7th profitable quarter in a row, and a positive cash flow of $5.2 million.

In 2022, Everspin reached record revenues of $60 million up 9% from 2022. In the year the company's cash flow from operation was $9.5 million, and the net income was $6.1 million.

Avalanche announces pre-production of its Gen-3 Space Grade Dual QSPI STT-MRAM solution for advanced SoCs and FPGAs

pMTJ STT-MRAM developer Avalanche Technology announced that its Gen-3 Space Grade Dual QSPI solution is now available in pre-production.

The devices are based on the company's latest generation STT-MRAM technology. Avalanche says that the new devices offer significant density, endurance, reliability, and power benefits, over existing memory solutions for aerospace and defense applications, particularly for easily configuring advanced SoCs and FPGAs, which are known to present complex design challenges.

Hprobe releases a new MRAM testing module to help increase production yields

Hprobe, a developer of testing equipment for magnetic devices, announced a new addition to its product line, the RF Pulse Module. The company says that this is the commercially available testing system to both collect statistics of error rate of the memory unit cell and take a deep look into switching dynamics of resistive memories.

Hprobe's IBEX system

Hprobe says that the RF Pulse Module is two orders of magnitude faster than existing devices and can help increase manufacturing yields. Hprobe has already begun shipping to tier-1 companies and major research institutes around the world.

Pagination

- Previous page

- Page 3

- Next page