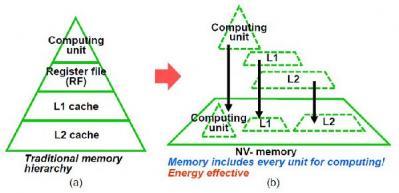

Toshiba announced a new computing architecture that uses only STT-MRAM to perform both operations and storage. The idea support computing capability, register file, primary cache and secondary cache all on the same perpendicular STT-MRAM, and Toshiba says it could lead to CPUs that are drastically faster and more efficient.

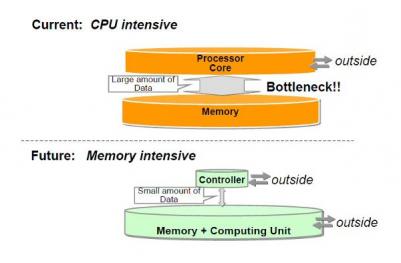

Toshiba explains that in the new architecture, the results of operations (answers) that correspond to combinations of certain inputs are prepared in advance in the form of a table and stored in the memory. In response to an input, an answer is read out of the memory. This is equivalent to an operation carried out by a CPU. Because the computation answer is read once, it drastically improves processing speed and power consumption.

Toshiba did some simulations and they say that a division process that requires 50 processing cycles with a normal CPU requires only 16 cycles with the new architecture. In another example, 408 cycles usually required to solve a quadratic equation was reduced to just 44 cycles! The simulations used Toshiba's 1-Mbit array that uses the company's 2T-2MTJ structure.

The new method requires results of operations to be calculated in advance (on an "external computer") - this is basically just like today's computer which use compilers. STT-MRAM is suitable for this architecture because of its high-speed and non-volatility.